- 类型:休闲益智

- 发行:KISS ltd

- 发售:2014年4月25日

- 开发:Coatsink

- 语言:英文

- 平台:PC

- 标签:

IBM试产5nm芯片:指甲盖大小可容纳300亿晶体管

- 来源:cnBeta

- 作者:Deego

- 编辑:Deego

当前商用晶体管栅极大小在 10nm 左右,但是 IBM 早已开始了 7nm、甚至 5nm 工艺的研究。不过为了制造 5nm 芯片,IBM 也抛弃了标准的 FinFET 架构,取而代之的是四层堆叠纳米材料。于是在指甲盖大小的芯片面积里,即可塞下大约 300 亿个晶体管,且能耗与效率都得到了保证。自 1970 年代以来,芯片行业在摩尔定律的加持下发展了几十年(每隔两年、芯片晶体管数翻一番),但近年来遇到了一些瓶颈。

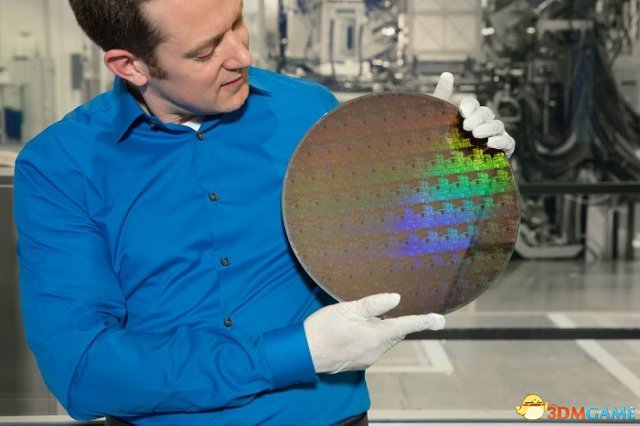

在纽约生产设施内测试的 5nm 芯片晶圆

在消费电子领域,14nm 芯片仍属于比较先进的标准,不过英特尔和三星的 10nm 工艺也已经向高端市场杀进。

研发方面,各公司也没有停下脚步,比如早在 2015 年,IBM 就携手 Global Foundries 和三星试产了一款 7nm 芯片。

该原型在指甲盖大小的面积里,塞进去了大约 200 亿个晶体管。得益于新工艺和新材料,其有望在 2019 年投入商用。

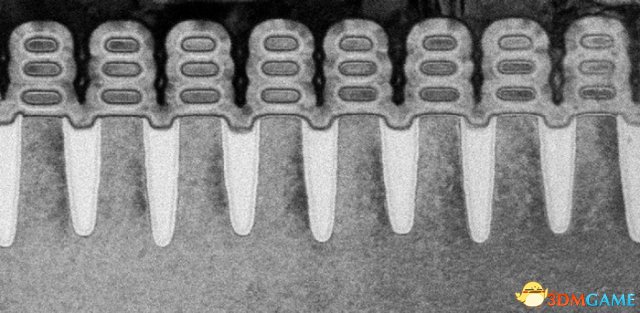

IBM 研究院 5nm 晶体管扫描图,其由堆叠硅纳米材料制成。

不过现在,IBM 公布了他们的下一步计划,将单个栅极的直径进一步缩减到 5nm,在同等面积下可挤下额外的 100 亿晶体管。尽管当前制造技术有潜力缩减至 5nm,但研究团队还是选择开发一种全新的架构。

自 2011 年以来,半导体行业采用 FinFET(鳍式场效应晶体管)工艺已有多年。恰如其名,它的样子有点像鱼鳍,三个载流通道被一个绝缘层所包围,但是这项技术也已接近可以缩小到的工艺极限。

研究员 Nicolas Loubet 手持一片新型 5nm 芯片晶圆

IBM 团队表示,继续缩减 FinFET,并不会对性能提升有太大的帮助。有鉴于此,他们在 5nm 芯片上采用了堆叠式硅纳米层,一次可向四个栅极发送信号(而不像 FinFET 那样一次只能向三个栅极发射)。

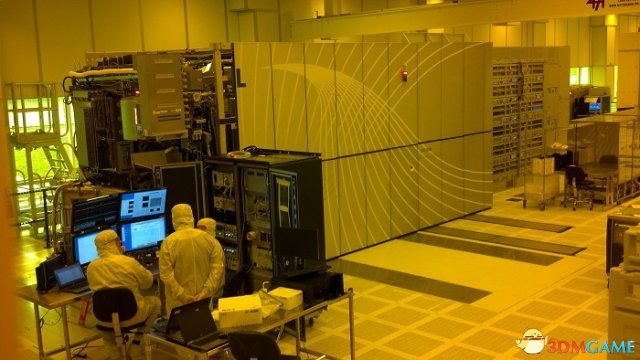

借助极紫外线光刻技术,他们可以在晶圆上绘制出更小的细节。与当前技术相比,它不仅光波能量高出许多,还支持在制造过程中持续调节芯片的功耗和性能。

与当前 10nm 芯片相比,5nm 原型芯片在额定功率下的性能可提升 40%,或在匹配性能下降低高达 75% 的能耗。

未来我们有望见到更多更小、更强大、更有效率的电子设备,不过当前 10nm 也才商用不久,7nm 要等到 2019,5nm 也还得再多等上几年。

玩家点评 (0人参与,0条评论)

热门评论

全部评论