深度分析国产龙芯新架构CPU:自主崛起 力拼英美

- 来源:驱动之家

- 作者:liyunfei

- 编辑:liyunfei

谈到国产CPU产品龙芯,围绕它最大的争议就是性能。虽然龙芯的早期产品并没有让大家满意,但随着新架构GS464E的披露,以及采用该架构的新一代CPU“3B2000”的正式问世,外界开始非常期待它倍增的性能究竟和Intel的主流产品存在哪些优势和差距。

在前一次《信息科学杂志》给出的数据测试结果中,早期编译的GS464E已经接近Intel、AMD现在市场上的主流架构性能,与Intel Core i3-550和AMD FX-8320基本相当,与Intel Core i5-2300略有差距,同时明显强于Intel Atom、VIA Nano、ARM Cortex-A57等低功耗架构。

而近日,《微型计算机》杂志6月刊中进行了更深入地分析。那么,龙芯的性能究竟到了何种地步,其设计水准距离国际竞争对手还差多远,龙芯选择MIPS究竟出于何种考虑,为何今日的龙芯不是基于现在的当红小生一ARM架构?针对这些外界争论多时的问题,本文将用专业而详尽的分析予以解答。

一黑一白,今日孰是孰非?

坦白来说,龙芯近年来在舆论中受到围攻已经不是新闻,今年初一篇名为《国产龙芯究竟水平如何?》的文章在网上掀起轩然大波,直指号称面向高性能服务器开发的龙芯3B-1500处理器尚不如今日ARM Cortex-A57手机处理器。

耐人寻味的是,不到一个月过后,该文的作者再次撰写了一篇《详解,新一代“龙芯”能否挑战Core i7?》,笔锋一转为尚未正式公开露面的下一代龙芯大唱赞歌。

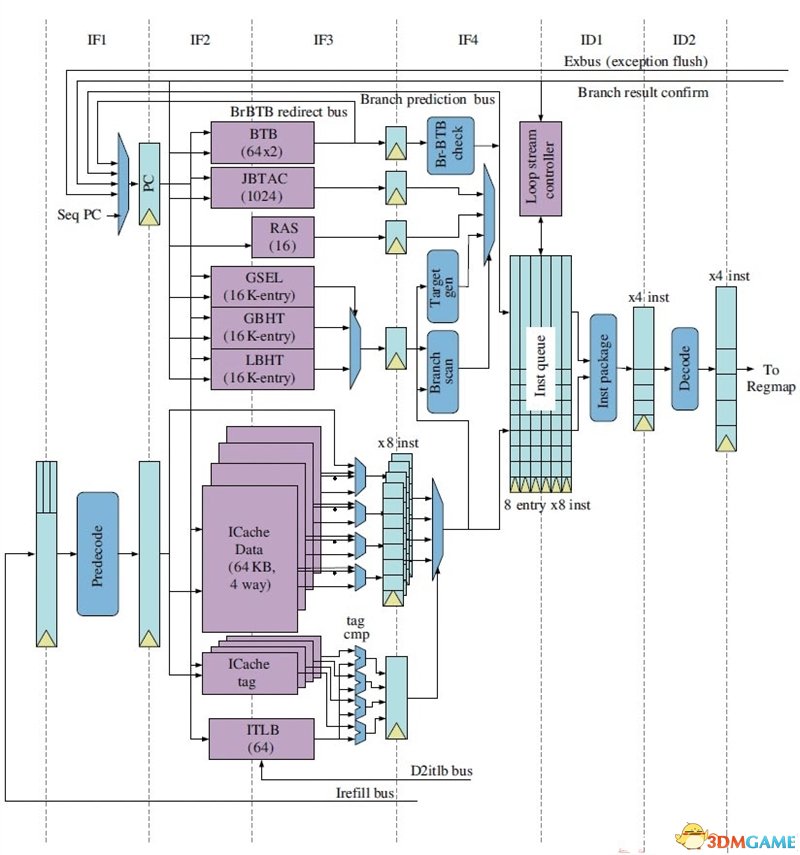

GS464E取指部件

在不诉诸阴谋论的前提下,笔者认为这样剧烈起伏的舆情其实都指向一个事实:对于龙芯的现状,其实外界并不了解,一般公众并不具备从龙芯组公开发表的艰深论文中推断其结构设计水平的能力,亦并不知晓编译器,相关软件系统与所用基准测试程序的偏好,因此对性能的对比也多有偏颇。

例如被抨击为不如Cortex-A57的龙芯3B-1500虽然流片于2012年,但其核心却是2006年左右完成的设计,当时其制定的竞争目标主要是Intel的奔腾3和早期奔腾4处理器,自然会落后于今日的手机CPU旗舰。

而被其描述为可以在IPC上与Ivy Bridge一战的新一代龙芯微结构GS464E,虽然相比上一代产品取得了突破性的进步,但在频率指标取得突破之前,又将凭借什么与Intel抗衡呢?

历史原因 为何选择MIPS指令集?

目前已经推出的龙芯核心主要分为三大系列,型号为GS1XX,GS2XXX和GS3XX,其中GS132系列对标ARM CortexM0和CortexM3,GS232和GS264对标ARM9,ARM11与Cortex-A12,GS464E也就是本文即将介绍的最新版龙芯核心,将对标Intel Ivy Bridge。

先前被认为不如手机CPU的龙芯3A 1000与龙芯3B1500均使用上一代GS464和其向量增强型GS464V核心设计,性能差距较大。

上述所有龙芯系列产品都兼容MIPS指令集,注意这里的兼容并不是如同外界谣传的那样指代龙芯使用了来自MIPS的核心,而是仅仅让龙芯的产品能够运行MIPS所定义的指令集,例如000000在MIPS中代表加法操作码,在龙芯处理器上也代表加法操作码,仅此而已。

硬件方面,从龙芯的微结构到电路、版图设计均为独立自主进行。

很多人也有疑惑,为何龙芯没有选择当下如日中天,隐隐与Intel形成分庭抗礼之势的ARM指令集呢?

其实龙芯项目开始前期调研的时间点是2000年前后,当时ARM的确有被列入考虑范围之内,但是面对龙芯要求实现高性能的初始目标相比,ARM公司的定位则显得不合时宜,彼时的ARM能拿出的最强核心设计是ARM11,没有乱序执行,没有多发射,没有今天这样先进的缓存系统。

ARM旗下第一款支持双发射的Cortex-A8设计是2005年才对外公布的,在此基础上加入乱序执行的Cortex-A9则更是到2007年前后才宣告面世。这倒不完全是因为ARM在高性能设计上实力孱弱,而更多地是因为ARM将自己的产品定位为面向嵌入式计算的产品,极为紧张的面积和功耗预算使得许多高性能设计上常见的特征难以实现。随着技术的进步以及嵌入式计算能力需求的暴增,ARM才开始着手打造高性能CPU。

GS464E微结构框架图,红色方框部分为乱序执行引擎

上世纪90年代,MIPS和DEC Alpha等几大厂商都于1995年前后陆续实现了乱序四发射的设计,风头甚至压过当时的Intel、MIPS的R4000、R10000以及DEC Alpha 21164。

其中21264放眼今日仍然是有志于处理器微结构设计的后学晚辈们所必看的经典之作,深度流水线,分支预测,寄存器重命名,Load-Store推测,一应俱全。虽然在90年代后期MIPS和DEC Alpha逐渐式微,但虎落平阳余威犹在。在x86阵营经营多年的专利壁垒无法攻破的情况下,高性能CPU厮杀的战场上为当时蹒跚起步的中国CPU提供的选择着实不多。

以当年的情况看,ARM在多年内都无力进攻嵌入式以外的市场,这意味着ARM的指令集系统在嵌入式以外几乎等同于无根之水,没有人会愚蠢到量产基于ARM11的个人电脑和服务器。单纯凭借一个国产项目力图对抗wintel联盟的铁桶江山与蚍蜉撼树别无二致。

而与Intel正面交战过并且曾经享有胜者头衔的MIPS和DEC Alpha所留下的软件生态环境自然要比ARM强大许多,国内先后上马的龙芯和申威两大拥有政府支持的CPU项目就是分别采用了MIPS与DEC Alpha指令集。

因此笔者认为,在坚持高性能设计并且想要获取市场支持的前提下,选择MIPS/DEC Alpha是一个正确的决策,以今日ARM的崛起来拷问当时的选择难免有马后炮的嫌疑,无人能够超越历史局限预估到十年之后的未来。

正像无人能够预见到2000年正踩在钢丝线上生死未卜的苹果公司能够在十年后登上浪潮之巅一样。但是历史终究已成历史,今日龙芯面临的困境也是众人皆知的,那么龙芯团队能不能实现自己当初的目标,他们拿出的新一代GS464E又是什么样的呢?

喜忧参半 新一代GS464E架构之前端取指

纵观全局,取指部件是新一代龙芯GS464E中改动最大的几个地方之一。大体框架上,一级指令缓存(取指部件图的下半部分)为了追求速度被设计为并行访问的结构,在IF2阶段和IF3阶段同时读取指令(IC Cache Data)和相关的地址标记(IC Cache tag),在IF4阶段判断是否命中,取出命中的指令。从取指部件部分的框架图来粗略判断,前端部分的效率仍是喜忧参半。

令人欣喜的地方有三个,在这三个方面龙芯GS464E的结构设计都达到甚至超越了国际水准。

第一,指令缓存的大小达到了64KB(四路组关联),超越了IBM Power7的32KB(四路组关联);

第二,取指宽度已经达到了每周期8条指令,考虑到龙芯以MIPS32作为基础指令集,以每条指令32位宽计算,一级指令缓存的取指宽度达到了每周期32字节,而Intel Haswell处理器的一级指令缓存仅能达到每周期16字节的吞吐率(但存储解码后指令的uop cache能达到32字节/周期的吞吐率);

第三,GS464E也加入了Intel从SandyBridge期间开始配备的循环检测器和循环指令缓冲区,这种结构设计允许CPU在不断取指令的同时,去识别哪些指令构成了一个循环,在发现循环再次出现的时候关掉指令缓存,仅从循环缓冲区中取用。笔者相信GS464E的循环缓冲区设计从Intel的SandyBridge中获取了一些灵感,巧妙地把它与负责解耦取指部分和解码部分的Instruction Queue做成了一个模块,与SandyBridge一样支持存储56条内层循环指令。

玩家点评 (0人参与,0条评论)

热门评论

全部评论